TSV 공정 서비스

TSV (실리콘 통공) 는 실리콘 채널이 스택을 구성하는 서로 다른 칩이나 층을 수직으로 통과하도록 함으로써 서로 다른 기능 칩의 통합을 실현하는 첨단 패키징 기술이다.TSV는 주로 구리 등 전도성 물질을 충전하여 실리콘 통공의 수직 전기 상호 연결을 완성하고, 신호 지연을 줄이며, 용량과 전기 감각을 낮추고, 칩의 저전력, 고속 통신을 실현하며, 대역폭을 증가시키고, 부품 집적 소형화의 수요를 실현한다.

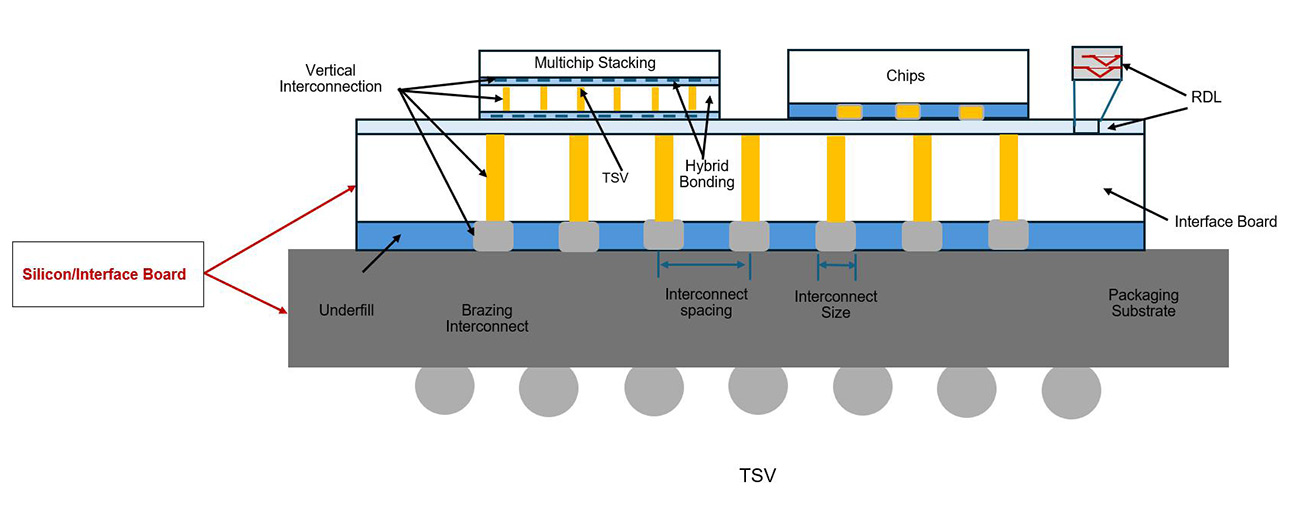

이전에는 칩 간의 대부분의 연결이 수평이었으며 TSV의 생성으로 여러 칩을 수직으로 스택하는 것이 가능해졌습니다.지시선 키 조합과 역장착 칩 볼록 블록은 파이프 코어 외부의 전기 연결을 제공하고, RDL (리디렉션 경로설정) 은 파이프 코어 내부의 수평 연결을 제공하며, TSV는 웨이퍼 내부의 수직 연결을 제공한다.

TSV는 주로 후면 연결, 2.5D 패키지, 3D 패키지의 세 가지 방향에 적용됩니다.

수직 후면 연결.단순한 후면 연결과 같은 칩 스택이 없습니다.TSV는 칩 후면의 용접 디스크에 연결하는 소스 코어에 있습니다.

2.5D 포장.튜브 코어는 실리콘 중개층에 연결되며 TSV는 중개층에 있습니다.

3D 패키지.TSV는 칩 스태킹을 위해 활성 코어에 있습니다.

프로세스:

구멍: 구멍을 만드는 것은 레이저 드릴링, 건식 식각, 습식 식각 등을 통해 완성할 수 있다.

절연층의 퇴적: TSV 구멍 내 절연층은 실리콘 기판과 구멍 내 전송 채널 사이의 절연을 실현하여 TSV 구멍 사이의 누출과 교란을 방지한다.

장벽 / 씨앗층의 퇴적: 동통은 2.5D TSV 층간 공정에서 TSV 통공의 내부 금속 상호 연결 재료로 자주 사용된다.

도금 채우기: 깊은 TSV 구멍을 채우는 것은 3D 통합의 핵심 기술로서 후속 부품의 전기 성능과 신뢰성에 직결된다.충전할 수 있는 재료는 구리, 텅스텐, 폴리실리콘 등이다.

CMP(화학 기계 광택): CMP 기술은 실리콘 표면에서 이산화규소 전매질, 차단층 및 결정층을 제거하는 데 사용됩니다.

웨이퍼 감소: 웨이퍼 표면이 평탄화되면 웨이퍼의 뒷면이 TSV를 노출하기 위해 얇아집니다.